## Make it for a Song!

# The New Maplin Matinée

Amazing Value For Only £299.95 + £99.50 for cabinet if required.

Easy to build. Latest technology - means less cost less components and 80% less wiring. Comparable with organs selling for up to £1 000 00 Two 49-note manuals. 13-note nedalboard All organ voices drawbars Preset voices: Banio, Accordion. Harpsichord Piano Percussion Piano sustain Sustain on both manuals, and pedalboard. Electronic rotor, fast and slow. Vibrato and Delayed vibrato Beyerh Manual and Auto-Wah Glide (Hawaiian Guitar Sound). Single finger chording plus memory. 30 Bhythms! 8-instrument voicing Major Minor and Seventh chords Unique walking bass lines with each rhythm. Unique countermelody line with each rhythm. Truly amazing value for money. Full construction details in Electronics & Music Maker magazine

The complete buyers' guide to electronic components. With over 300 pages, it's a comprehensive guide to electronic components with thousands of photographs and illustrations and page after page of invaluable data. Get a copy now—it's the one catalogue you can't afford to be without.

| I enclose £1.:<br>Name | 25. | E4/8 |

|------------------------|-----|------|

| Name                   |     |      |

\_\_\_\_\_

Post this coupon now for your copy of our 1981

THE PARTY OF THE P

## MIRPLIN

Maplin Electronic Supplies Ltd. All mail to: P.O. Box 3, Rayleigh, Essex SS6 BLR Telephone: Southend (0702) 554155. Sales (0702) 55291

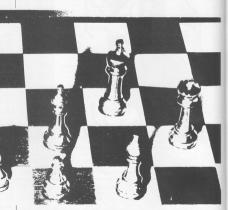

J59-161 King Street, Hammersmith, London W6. Telephone: (01) 748 0926 284 London Road, Westcliff-on-Sea, Essex. Telephone: Southend (0702) 554000. Both shops closed Mondays. The chess computer described in this article plays a good game It is designed around Intel's new 8088 16-bit microprocessor and features both reasonable speed and reasonable intelligence. Being able to play at various levels of skill, it will make a worthy opponent for many chees enthusiaste

an electrical measuring circuit it will serve a variety of purposes, besides

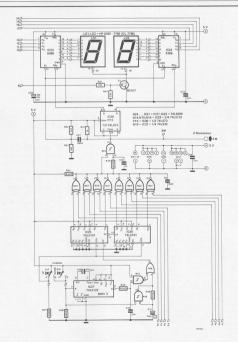

Last month, the basic principles of the logic analyser were explained with

the aid of block diagrams. Now the moment has arrived to see what the

actual circuit diagrams look like. Again, the unit has been split up into two

sections: the logic analyser itself and the cursor circuit. This makes it

easier to 'place' the various parts previously shown in the block diagrams. crystal-controlled stroboscope .....

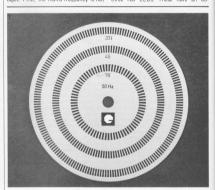

It is common practice for record player manufacturers to include a stroboscope with a speed calibration disc. This is very cheap and extremely accurate - especially if it is crystal-controlled. Find out how to make your

advertisers' index .....

Here are a few healthy recipes to keep you and your computer in good

Detecting hymidity involves a great deal more than meets the eye I Intil recently, the few reliable devices available were too complex for widespread use. This article presents a humidity sensor that has many advantages, despite its unsophisticated circuitry. Incorporated directly into

we haven't forgotten the TV games computer!

which it is easy to operate maintain and calibrate

4.10 4-19

4.21

4.22

4-26

4-28

4-32

UK-20

EDITOR-W. ... der Heret

E. Krempelsaue

LIK EDITORIAL STAFF T. Day E. Rogans D Milliams

alaktas april 1991 - IIV.03

TECHNICAL EDITORIAL STAFF J. Barendrecht G H K Dam P Holmes

G Nachhar Nachtmann K S M Walrayen

### SPECIAL SUPPLEMENT:

shape until Book Two arrives market ....

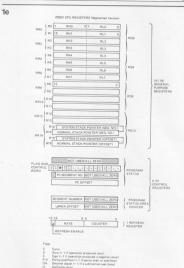

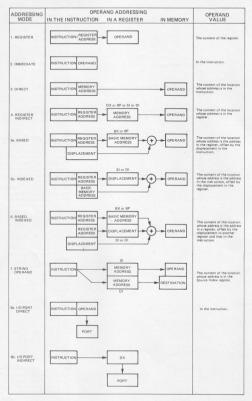

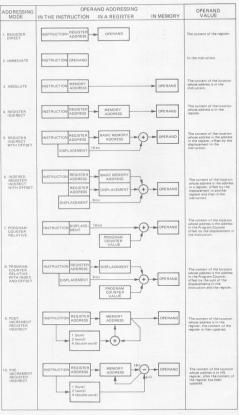

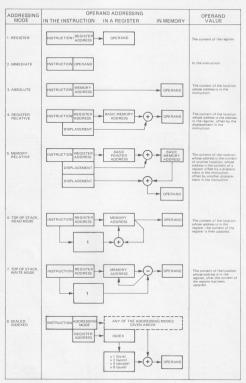

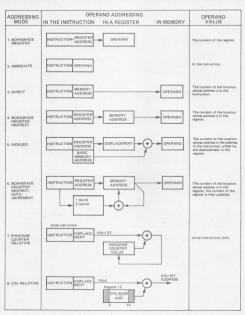

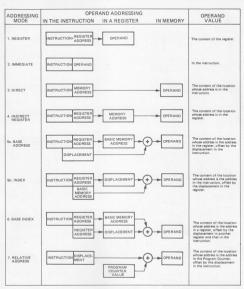

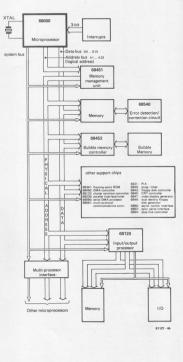

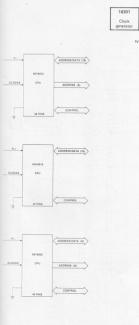

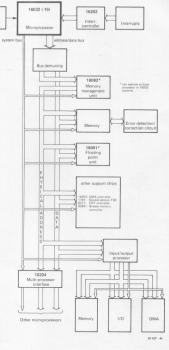

#### 16-bit microprocessors

own

The pace of present-day developments in computer science is amazing. Now even 16-bit 'micro' processor systems are integrated on a single chin and already equal, if not surpass, modern 'minicomputers'. This means that a full-fledged personal computer is within any enthusiast's reach. The only problem is: which one? This article gives a survey of the available types and discusses the pros and cons of each particular system.

**New! Sinclair ZX81 Personal Computer.** Kit: £49.95 complete Silvicial

Reach advanced computer comprehension in a few absorbing hours

1980 saw a genuine breakthrough - the Sinclair 7X80 world's first complete personal computer for under £100 At £99.95, the ZX80 offered a specification unchallenged at the price Over 50 000 were sold and the

ZX80 won virtually universal praise from computer professionals

Now the Sinclair lead is increased: for just £69.95, the new Sinclair 7X81 offers even more advanced computer facilities at an even lower price. And the 7X81 kit means an even bigger saving. At £49.95 it costs almost 40% less than the ZX80 kit!

Lower price: higher capability With the ZX81, it's just as simple to teach vourself computing, but the ZX81 packs even greater working capability than the ZX80. It uses the same micro-processor.

but incorporates a new, more powerful 8KBASICROM - the 'trained intelligence' of the computer. This chip works in decimals, handles logs and trig, allows you to plot graphs, and builds up. animated displays. And the ZX81 incorporates other

operation refinements - the facility to load and save named programs on cassette, for example, or to select a program off a cassette through the keyboard.

Higher specification, lower pricehow's it done?

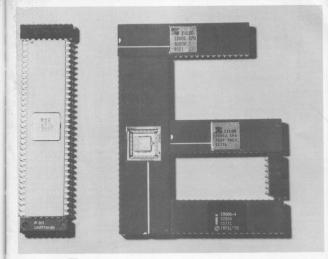

Quite simply, by design. The ZX80 reduced the chips in a working computer from 40 or so, to 21. The ZX81 reduces the 21 to 4!

The secret lies in a totally new master chip. Designed by Sinclair and custom-built in Britain, this unique chip replaces 18 chips from the ZX80!

Proven micro-processor, new 8K BASIC ROM, RAM-and unique new master chip.

complete

Kit or built it's up to you!

The picture shows dramatically how easy the ZX81 kit is to build: just four chips to assemble (plus, of course the other discrete components) - a few hours' work with a fine-tipped soldering iron. And you may already have a suitable mains adaptor - 600 mA at 9 V DC nominal unregulated (supplied with built version)

Kit and built versions come complete with all leads to connect to your TV (colour or black and white) and cassette recorder

New Sinclair teach-vourself BASIC

manual Every ZX81 comes with a compre-

BEBBBBBBB

hensive, speciallywritten manual -a complete course in BASIC program-

ming, from first principles to complex programs. You need no prior knowledge -children from 12 upwards soon become familiar with computer

operation.

# New, improved specification ■ Z80A micro-processor – new faster version of the famous Z80 chip, widely recognised as the best ever made

Unique 'one-touch'

key word entry:

the ZX81

eliminates a great

deal of tiresome

typing. Key words

(RUN, LIST, PRINT,

etc.) have their own

single-key entry.

O Unique syntaxcheck and report codes identify programming errors immediately.

Full range of mathematical and scientific functions accurate to eight decimal places

- Graph-drawing and animateddisplay facilities.

- Multi-dimensional string and numerical arrays.

- Up to 26 FOR/NEXT loops.

- Randomise function useful for games as well as serious applications.

- Cassette LOAD and SAVE with named programs.

- 1K-byte RAM expandable to 16K bytes with Sinclair RAM pack.

- Able to drive the new Sinclair printer (not available yet but coming soon!)

- Advanced 4-chip design: microprocessor, ROM, RAM, plus master chip - unique, custom-built chip replacing 18 ZX80 chips.

Sinclair Research Ltd, 6 Kings Parade, Cambridge, Cambs., CB2 1SN. Tel: 0276 66104. Reg. no: 214 4630 00

### lf you own a Sinclair ZX80

The new 8K BASIC ROM used in the Sinclair ZX81 is available to ZX80 owners as a drop-in replacement chip. (Complete with new keyboard template and operating manual)

With the exception of animated graphics, all the advanced features of the ZX81 are now available on your ZX80-including the ability to drive the Sinclair ZX Printer.

## Coming soonthe ZX Printer

Designed exclusively for use with the ZX81 (and ZX80 with 8K BASIC ROW), the printer offers full alphanumence with the prints out exactly what is on the whole TV screen without the need for further instructions. The ZX Printer will be available in Summer 1981. At around £50 – watch this space!

To: Sinclair Research Ltd, FREEPOST 7, Cambridge, CB2 1YY.

# 16K-BYTE RAM pack for massive add-on memory.

Designed as a complete module to fit your Sinclair ZX80 or ZX81, the RAM pack simply plugs into the existing expansion port at the rear of the computer to multiply your data/program storage by 16!

Use it for long and complex programs or as a personal database. Yet it costs as little as half the price of competitive additional memory.

How to order your ZX81 BY PHONE – Access or Barclaycard holders can call 01-200 0200 for personal attention 24 hours a day, every day. BY FREEPOST – use the no-stampneeded coupon below. You can pay by cheque, postal order, Access or

Barclaycard.

EITHER WAY – please allow up to 28 days for delivery. And there's a 14-day money-back option, of course. We want you to be satisfied beyond doubt – and we have no doubt that you will be.

| Qty   | Item                                                                                                       | Code     | Item price | Total      |

|-------|------------------------------------------------------------------------------------------------------------|----------|------------|------------|

|       | Sinclair ZX81 Personal Computer kit(s). Price includes<br>ZX81 BASIC manual, excludes mains adaptor.       | 12       | 49.95      |            |

|       | Ready-assembled Sinclair ZX81 Personal Computer(s).<br>Price includes ZX81 BASIC manual and mains adaptor. | 11       | 69.95      |            |

|       | Mains Adaptor(s) (600 mA at 9 V DC nominal unregulated).                                                   | 10       | 8.95       |            |

|       | 16K-BYTE RAM pack(s).                                                                                      | 18       | 49.95      |            |

|       | 8K BASIC ROM to fit ZX80.                                                                                  | 17       | 19.95      |            |

|       | close a cheque/postal order payable to Sinclair Resease charge my Access/Barclaycard account no.           | arch Ltd | , for £    |            |

| *Plea | ase delete/complete as applicable.                                                                         |          | Ple        | ease print |

| Nam   | e: Mr/Mrs/Miss                                                                                             | LIT      | 1111       | 11         |

|       |                                                                                                            |          |            |            |

| Addr  | ess                                                                                                        |          |            |            |

|       |                                                                                                            |          |            |            |

| FREE  | POST - no stamp needed.                                                                                    |          |            | ELK04      |

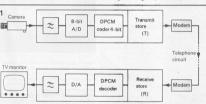

Private TV by public telephone

Conventional television signals are very

expensive to transmit over landlines,

because the signal occupies such a large

part of the electromagnetic spectrum

that costly circuits and cables have to be

used. British Television and the control of the

that costly circuits and cables have to be

added to the control of the control

has developed a cheaper, digital slowscan television system which uses the

two-wire domestic telephone line and is

now being tried out in many different

applications. For example, TV conferpress can be set up by dislinin-out and

distant radar displays are being made

available at a port control office using evisting lines If the cost of sending a television signal over considerable distances by landline were small, there would be many more commercial applications in which it could play an important part Obvious examples are remote surveillance of widely dispersed sites and obviating a lot of travel by holding 'video' conferences. But conventional television is exceedingly expensive to transmit by line because of the very large bandwidth of the basic signal: that is the range of frequencies that the signal takes up in the electromagnetic spectrum uncomfortably big. A 625-line television signal occupies a hand 5% MHz wide more than five times the width of the entire medium-wave broadcast hand This means that to send a TV signal over

distances greater than a few hundred metres by line requires special cables to be laid, and for trunk connections a stellite or a chain of microwave radio links may have to be used. The capital and operating oosts of such systems are usually so high that only rarely can an when alternative arrangements will do. For some years, British Telecom (the British Telecom the British Telecommunications part of the

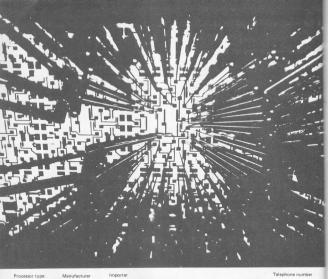

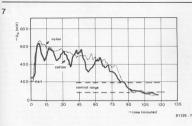

Post Office) has been studying ways of reducing the cost of television transmission in an effort to make more applications economically attractive All the techniques out forward inevitably compromise the quality of the display in some way (that is, they send less information than the basic TV signal is canable of carning) and therefore call into question the accentability of such displays for various purposes: in each case the suitability can be judged only by trial under realistic circumstances Industrial development has been started on a range of novel equipment including slow-scan TV converters, narrow-hand (1-MHz handwidth) TV equipment video-conference terminals and real-time picture-compression converters and over the next two to four years will be conducting trials ...tale to private --nublic-sector companies which have suitable applications

The first of these developments to go into production and on practical trials is a slow-scan TV system which operates over the public telephone network or any data circuit

#### Reduction

Beause conventional television signals cocupy a bandwidth equivalent to almost 2000 telephone circuits, a great deal of compression of that frequency range is obviously needed. There are three distinct ways of achieving that aim. In increasing order of complexity, and therefore cost, it be when the control of the contro

In the present system the most significant reduction is in speed for many purposes it simply is not necessary to transmit the usual 25 frames every second, so an immediate reduction of 100 or 1000 times is realized by taking four or 40 seconds respectively to send one image. A further factor of five is achieved by reducing the clarity, through sending only one complete set

of scanning lines, or field, instead of two interlaced sets per frame as in broadcast TV, and limiting the horizontal resolution (along the scanning line) to about 210 visible points per line.

In conventional TV cameras and monitors the signal representing one field is generated and displayed in 20 milliseconds It follows that to make a discrete field available for transmission and viewing over a much longer period. a nicture store must be provided at both the transmitting and receiving terminals At the start of a sequence or upon an alarm or other command, a TV field is cantured in the transmitting and store From there it is sent at a rate determined by the available bandwidth of the transmission network to the identical receiving-end store tho contents of which are continually displayed on the monitor. The observer therefore sees each new nicture gradually over-writing the previous one from left to right, which is why we call the technique slow-scan TV

#### Digital System

Slow-scan TV is not new Analogue systems in which the video-signal wave is carried over voice-band telephone lines have been on the market for some years. They suffer from accumulation of noise, especially over long distances where slow-scan TV offers the greatest savings Distortions also show up directly Digital transmission systems in which the analogue waveform is encoded as a series of digital pulses of equal amplitude do not suffer these defects; provided digit errors in transmission are infrequent, the quality of picture is independent of the distance travelled Moreover with the advent of silicon-chin TV digitizers and cheap digital memories the terminals match much better to digital transmission than they do to analogue. There is also scope for the third category of picture reduction, that is, removing some redundant information from pictures which have already been translated into digital code

In our equipment, only relatively simple encoding is used. The picture is expensive to provide over any great distance, their use tends to be in the

Figure 1. In television broadcasting, one complete picture field is generated and displayed in 20 milliseconds. To make a field available for transmission and viewing over a much longer period, picture stores must be used at both terminals, as in the above block diagram of a typical system. Listed below are various applications selected for system trials, Applications 1 to 9 can be classed as remote surveillance systems, with transmission in one direction only and the transmitter usually unmanned. The rest use two-way communication, though not necessarily involving the transmission of pictures in both directions. They work on voice-hand telephone lines with a bandwidth restricted to about three kilohertz.

range of only a few kilometres where transmission can be over ordinary cantured as 200 sean lines, each contain ing 210 visible picture elements (pels) When speech is encoded for telephone communication 8-digit 'words' are used to convey information about the original speech waveform. This is known as 8-bit pulse code modulation (PCM) Here each nicture element is encoded as a 4-bit word which represents the difference between that nel and the one immediately above it in the nicture In this way both nicture stores are only half the size that they would be for 8-hit PCM Transmission time is halved too: picture quality, of course (at least to the practised eye), is slightly reduced. In the receiver terminal the 4-bit differential words are decoded to 8-bit PCM before display, and field-repeating is necessary to feed the conventional

By further extending the coding scheme we can reduce the 4-bit words to an average of two to three bits, depending on the content of the picture. However there is a good prospect that in later generations of slow-scan systems more complex processing will eventually reduce the average information to perhaps between half a bit and one bit per sample, with a corresponding reduction in time before the next frame can be displayed to keep the picture un to date

625 Jine TV monitor

The use of entirely digital apparatus has the additional advantage that it can be matched to any digital circuit. So while a good quality voice-band circuit can support a data rate of 9-6 kbit/s, giving a picture time of 15 to 25 seconds an international circuit accepting subscriber dialling will be slower than that. On the other hand, a private wire or a

'nacket-switched' system in which data is stored and then transmitted rapidly when the user's turn in the traffic queue comes round may be a good deal faster So digital slow-scan is considerably versatile in the way it fits into existing telecommunications networks

#### Annlications

Recause of the cost of terminal equipment slow-scan TV is not appropriate to short distances for it is then prob ably cheaper either to install a special cable or to use 313-line TV signals over telephone lines with repeating amplifiers at intervals of say 1% km or less In fact such a system is included in plans for other visual-service trials But for applications where service must be provided at short notice, or only temporarily, slow-scan TV may be attractive if the resolution and un-date time are acceptable. The same is true of connections longer than a few kilometres, where conventional TV becomes too costly or impractical

To study how well it works various applications have been selected for trials. Systems in operation or already planned are listed in the table on page 13. The upper group can be classed as remote surveillance: the systems are uni-directional with the transmitting end usually unmanned Some are permanently in operation, but those using dial-up circuits, in which communication over the link is set up by dialling over the telephone either in a private network or in the public system require an automatic-answering or alarmtriggered automatic-dialling device. In a minority of applications the transmission rate is 48 kbits/s, highly desirable from an operational view-point

> Transmission 4-8 kb/s dial-up on PSTN

> 4-8 kb/s dial-up on PSTN

48 kb/s on metallic pair 4-8 kb/s dial-up on PABX

48 kh/s on repeatered pair

48 kb/s on metallic pair

4-8 kh/s dial-up on PSTN

4-8 kb/s dial-up on PSTN

4.9 kb/e dial-up on PSTN

4-8 kb/s dial-up on PSTN

4-8 kb/s dial-up on PSTN

Figure 2. Examples of the quality of various pictures received over digital slow-scan TV systems. In the two to the left, a new picture is gradually over-writing the previous one from left to right, Prolonged tests are being carried out to assess acceptability in practice and findings will be made available late in 1981,

### Table 1

### Application

| 1 | Protecting radio station after terrorist threat | 5 km     |

|---|-------------------------------------------------|----------|

| 2 | Detecting illegal dumping; rapid installation,  | 2 - 3 km |

- temporary use 2 Protecting bullion vault Security monitoring of premises at night from two cameras on one system

- Monitoring road traffic for control of signals Extension of radar displays to port control office

- Underwater surveillance from submersible craft (via ultrasonic transmission link) Security monitoring of premises at night,

- from one place Occasional access to remote camera for

- traffic control 10 Sending X-ray pictures from hospital to

- consultant Editorial submission to upper management Liaison between processing plants

- Aid to project collaboration between laboratory and contractors Conferences between people in various places 250 km 14

- Conferences between people in various places Conferences between people in various places 200 km

- Editorial conferences between newspaper

offices

150 km 4-8 kb/s dial-up on PSTN 40 km 48 kb/s on private groupband 4-8 kb/s on private telephony

Dietance

5 km

25 km

10 km

400 km

20 km

100 km

80 km

200 km

120 km

4-8 kb/s on private circuit 150 km

because the un-date time is only five seconds, but because such circuits are telephone wire pairs. If necessary for greater distances amplifiers are used at intervals of shout 10 km to maintain signal strength. The only likely use over greater distances is where a so-called 'grouphand' circuit with a handwidth of 48 kHz is already available for other purposes but can be taken over when it

is idle All the other systems are on voice-hand circuits that is with handwidthe of about three kilohertz. Although this means the nicture eneeds have to be slower such circuits are by far the most readily available especially if dial-up access to the telephone network is accentable. Not surprisingly many security-surveillance systems are not needed during working hours, but their continuous use of lines and switch outlets at night, when not needed for other traffic makes for economical use

of those resources The lower group in the table involves two-way communication, though not necessarily sending pictures both ways (see applications 10 and 11) The main use is as an aid to working discussions hetween neonle in different places but closely involved with the same project product or service. It is in these 'conferencing' applications that there is greatest room for doubt about the quality and speed of the picture. The restricted resolution of 210 x 290 visible pels is thought to be good enough for sketches diagrams many (hut not all) X-ray pictures newspaper lay-outs and views of most solid objects such as printed circuit boards, but it does not reproduce 200-mm lines of typescript well enough for comfortable viewing: it remains to be seen how often this becomes a disadvantage in practice. It is, of course, technically feasibly to make a slow-scan system of, say, 420 x 580 pels but the transmission time becomes four times longer, which is perhaps an even greater detriment to conference applications

Few people who are likely to use slowscan TV in Telecom trials or in the first years of a public service are familiar with the form of picture presentation, Many react quite favourable at first contact, tending not to notice the lower resolution nor to condemn the slow speed or lack of colour. But it is now becoming apparent that such spontaneous opinions are a poor guide to the true worth of the system. Consider the frustration of the security man who feels sure something is in need of attention but must wait 50 seconds to be absolutely certain, or of the energetic designer who wishes to display several modifications to his sketch in quick succession.

#### Feed-back

Only a prolonged test in the service for which it is intended can give a reliable indication of how acceptable a system is for a particular job. The economics of the system too can be assessed only against alternative ways of performing the same essential task such as having a security quard at the site to be protected This means that feed-back from people trying the system out usually after they have been using it for at least six months is vital to Telecom's

visual-service trials In addition, experience of the engineering requirements is a valuable pointer to the directions that further system developments should take It has already been found, for example, that means for camera selection and other forms of control probably by momentarily reserving the data flow, would greatly improve the value of a system for surveillance work as would an ability to detect movement

The findings of our slow-scan television trial will be summarized in a report late in 1981 a digest of which will be released to interested organizations. The outcome promises to be a profitable

new nublic service Dr N.D. Kenvon

British Telecom Research Laboratories Martlesham Heath

#### Bocket to inner space

The 30-meravolt vertical tandem Van de Graeff accelerator due to come into use early this year at the UK Science Research Council's Daresbury Laboratory near Liverpool is the largest in the world and will provide eciantiete with a noval means of studying nuclear matter Known as the Nuclear Structure Facility (NSF), it will be used mainly to accelerate heavy ions. Collisions of heavy ions are predicted to be canable of generating shock waves in which abnormally high-density matter may be created such as exists only in the cores of neutron stars. This view is of the 41-metre high-voltage column looking down past the centre high-voltage terminal to the base the nicture was taken before the intershield was fitted

Finding matching transistors is a highly unpopular and tedious occupation. Nevertheless, it is one of those jobs that upon the control of th

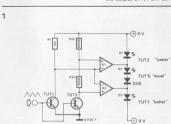

Elektor has now come up with a shortcut in the form of a transistor tester. It makes life a lot easier, as it actually compares two transistors. LEDs light to indicate whether their UBE and HFE correspond or not. The circuit does all the work — you just plug in transistors and watch the LEDs. There are three LEDs altogether: one to indicate that sample no. 1 is "better" than no. 2, one to indicate the opposite and another to show the aris is a perfect match.

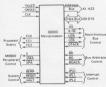

#### Operation

All this may seem rather complicated, but in actual fact the sters is based on a fairly straightforward principle. Figure 1 shows a simplified version of the circuit to make matters clear. A triangular wave-shape is applied to the transistors under test (TUTs). Any differences between their collector voltages are detected with the sil of two comparations of the collector of the comparation of the comparation of the comparation of the comparation of the collector of the comparation of the collector of the collec

Now to put it into practice. As shown in figure 1, the two TUTs are driven by exactly the same control voltage, but their collector resistors are marginally different. R2<sub>a</sub> and R2<sub>b</sub> together are slightly greater in value than R1, whereas R2<sub>a</sub> alone is a little smaller than R1. And that is the whole trick of

the tester circuit Let us suppose the two TUTs are identical as far as their URF and HFF are concerned. The rising slope of the input voltage will then switch them both 'on' at the same time and the voltage at their collectors will drop If we were to freeze the action at any point, we would see that TUT2's collector voltage is a tiny bit lower than that of TUT1, due to its total collector resistance being slightly greater. Since. on the other hand, R2a is a little smaller in value than R1, the voltage at the R2a/R2b junction will be slightly higher than that at the collector of TUT1. As a result of this, the '+' input of comparator 1 will be positive with respect to its '-' input. This means that the output of K1 will be high and LED

# Transistor match-maker

### A transistor tester for finding matched pairs.

'Oh no, not another transistor tester!' may well be several readers' initial reaction. Don't worry, this article is designed to save you and vigour eyes hours of strain and boredom. The device is capable of picking matched transistor pairs from a whole pile of 'possibles', and all within seconds. Two transistors will be 'matched' if their base/emitter voltage and their current amplification are the same. The degree of accuracy may range from 'roughly the same' to 'identical' (1%) and can be adjusted, as required, It really is an indispensable aid when suitable matched transistors are needed for differential amplifiers, or temperature ensors.

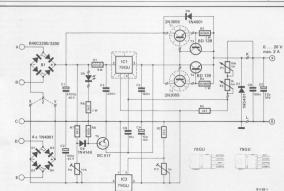

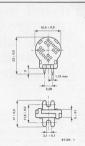

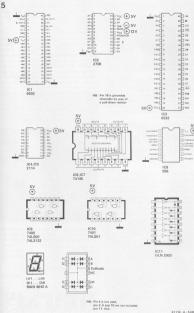

Figure 1. The simplified circuit diagram of the transistor tester. Comparators check the two transistors for differences in voltage and the result is indicated by the LEDs.

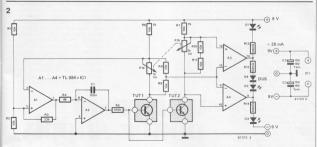

Figure 2. The final version of the circuit diagram, It is built around a set of four opamps. Two (A1 and A2) constitute the triangular wave generator and the other two act as comparators.

D1 will not light. At the same time, the '4' input of K2 is negative with respect to its '-' input and so its output will be low and LED D3 will not light either. In this situation, where K1's output is high and K2's is low, D2 will light up as an indication that the two transistors are in fact identical.

Now let us see what happens when to TUT1 has a lower Uge and/or a higher TUT1 has 10 mer Uge and/or a higher HEE than TUT2. During the positive dege of the triangular singal, the voltage at the collector of TUT1 will drop sooner and/or faster than that of TUT2. Comparator KI will react to this in the same manner as before, in that the respect to the "-" input and its output will therefore be high. Since TUT1's low collector voltage is also connected to

the '-' input of K2, that particular '-' input will now be lower than the '-' input will now be lower than the '-' input connected to TUT2's collector. This will cause the output of K2 to rise. Since the two comparator outputs are high. D1 will not light. D2, like D1, will and the wind be to light their and cow there is nothing to stop D3 from lighting. D3's LED will therefore indicate that TUT1 is the 'better man' of the two transistors.

If TUT2 turns out to be 'better', this will of course cause its collector voltage to drop at a faster rate. As a result, both the voltage at the collector itself and that at the R2<sub>a</sub>/R2<sub>b</sub> junction will be lower than the collector voltage of TUT1. This means that the '+' inputs of the comparators will both become low

#### Parts List

Resistors: R1,R2,R8 ... R11 = 10 k

R3 = 33 k R4 = 1 M R5 = 100 k R6,R7 = 10 k 1% R12 R13 R14 = 680 Ω

P1 = 1 k tandem potentiometers, linear

Capacitors: C1 = 100 n C2 C3 = 10 u/16 V

02,00 - 10 µ/10 V

Semiconductors: IC1 = A1 . . . A4 = TL 084 D1 . . . D3 = LED

D1 . . . D3 = LED D4 = DUS

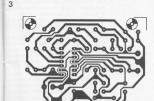

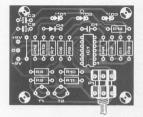

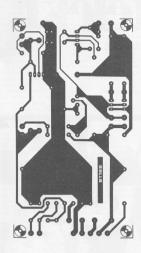

The component overlay and track pattern of the tester printed circuit board. Reliable sockets should be used for the two TUTs.

with respect to the '-' input so that the two outputs will be low. This prevents D2 and D3 from lighting and this time it is D1 that lights to indicate that TUT? is the 'hetter' choice

#### The circuit diagram and the printed circuit hoard

Figure 2 shows the complete circuit diagram of the tester. All it consists of is a single IC type TI 084 which contains four EET onamns Schmitt trigger A1 and the integrator built up around A2 combine to form a simple triangular wave generator. This provides the voltage. The other two onemns (A3 and AA) act as comparators and it is their outputs which control the LED indications, D1 . . . D3.

A closer look at the conglomeration of resistors in the collector leads of the two TITs will evoluin why we used a simplified version of the circuit to clarify the principle. The final circuit looks much more complicated, as a tandem not (P1) has been added to preset the range within which the transistors may be considered to be identical. If P1 is turned left as far as it will go and the middle LED (D3) lights. the two TUTs will be identical within about 1%. The 'matched pair' criterion is relaxed to about 10% tolerance when the not is turned fully clockwise.

The maximum possible accuracy is limited by the tolerance in R6 and R7 by the offset voltage of the TL 084 and by the tracking accuracy of P1a and P1b. In addition, the transistors under test will react to changes in their temperature, which is something to watch out for. If, for example, a transistor is held in the hand and then inserted in the tester the results of the test will be affected, and so it is better to wait until it cools off again before jumping to conclusions

The tester requires a symmetrical power supply. The level of the supply voltage is not critical and the circuit will not only work well at the indicated + and -9 V. but also at + and -7 V or even at + and -12 V. The circuit can easily be powered from two 9 V batteries as its current consumption is only 25 mA and, in any case, the tester is hardly likely to be switched on for hours on end. Being battery fed, the circuit can be constructed into a neat, compact device and is therefore easy to work

Figure 3 shows the tester's printed circuit board. It is difficult to see how anything could go wrong (touch wood!). considering the small amount of components required. All that it needs are a single IC, two transistor sockets for the TUT's, a few resistors and three LEDs. Make sure resistors R6 and R7 are 1% types.

An adjustable power supply can of course he designed in a number of ways To start with it could be constructed with discrete components only and there are many standard recines which cater for this The problem is however that a reasonable size nower supply requires quite a few discrete components so that such circuits and up being highly complicated Quite unnecessary, in the chin age

A quick and inexpensive solution provided the supply only has to deliver fairly low currents is to use integrated

# universa power supply

As regular readers will agree. ample space and attention has heen devoted to nower supplies on Flektor's pages in recent years They have become one of the decigner cuisine's enecialities en to speak Our September '80 issue for instance featured the precision power unit a very neat accurate device that can also act as a reference voltage source This time Flektor wishes to cater for more universal tastes and has therefore produced a less exclusive. but highly popular power unit: a cheap, straightforward, multi-

nurnose experimental supply that

can be adjusted between 0 and

voltage regulators. As soon as higher currents are involved however the price of integrated regulators also tends to go up which brings us back to square one

That is why a compromise must be sought: a reasonable quality power supply without breaking the bank. This particular power supply is a step in the right direction. It combines a few chean integrated low-power regulators and several series transistor 'heavies'. The ICs stabilise and control the voltage without complicating matters and the transistors provide the required number of amos

Since the supply voltage of most circuits rarely exceeds 18 . . . 20 V, the upper voltage threshold has been chosen at 20 V If a higher voltage is required (to test amplifiers for instance) two power supplies may be connected in series We'll come back to how that is done later Besides a double power supply has considerable advantages as more and more circuits nowadays need both a positive and a negative voltage, A double version is therefore to be recommended for experimental purnoses

One of this circuit's greatest attributes is that its lower voltage threshold is really and truly 0 V - a commodity which very few other circuits can boast, Because of the large voltage range, provision has been made for both coarse and fine adjustment of the output voltage. Any experimental nower supply will, of course, have to be short-circuit proof and this is certainly the case here, However, no arrangement was made for a presettable current limitation, as this would only serve to complicate matters and, in any case, experience has shown that this 'luxury item' is hardly ever used.

The supply can deliver up to 2 A plenty for most applications, Furthermore, the power supply features a very low ripple voltage due to the IC's high

output voltage:

20 V

output current:

0 . . . 20 V coarse and fine adjustment short-circuit current: about 2,3 A ripple < 1 mV (at full-load)</li>

1

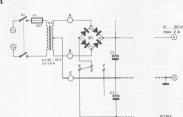

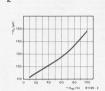

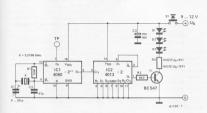

Figure 1. The circuit diagram of the power supply, IC1 is the main voltage regulator and IC2 provides a negative bias voltage enabling the output to be adjusted down to 0 V.

'ripple rejection' (70 dB). It will not exceed 1 mV over the full range of output current and voltage.

#### The circuit diagram

As figure 1 shows, the power supply circuit really inst' that complicated. In all fairness, this is not the complete version. We have omitted the 'front-end', because the transformer(s) and bridge rectifier B1 and D1..., D4 may be connected in various ways, according to the supply's purpose. This aspect will be dealt with further on in the article. The rectifier and smoothed transformer.

voltages appear across C1 and C2. The higher of the two goes, via R1, to the heart of the circuit: IC1, a four-pin 78GU voltage controller in a 'power watt' case. Normally speaking, the common input of the IC should be grounded, giving a minimum output voltage of 5 V. As it would be nice to have the lower voltage threshold at 0 V. however, the common input is connected to a -5 V negative voltage in this circuit. This negative bias voltage is obtained from the second voltage regulator (IC2) and is adjusted with P3, The output of IC1 is buffered by two emitter followers (T1 and T2) that are connected in parallel to provide a maximum output current of 2 A. The output voltage can be coarsely adjusted with P1 between 0 and 20 V: P2 provides the fine adjustment.

T3 and T4 ensure short-circuit protection. As soon as the output current exceeds 2 A, the voltage across R3 and

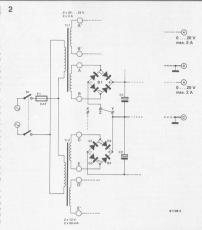

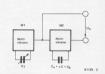

Figure 2. The transformer and bridge rectifier section when a double power supply is built up on two boards.

3

Board 1

Board 2

Board 2

P4 reaches the point where T2 and T4 will start to conduct. This causes the nower supply load to be directly connected to the output of IC1 IC1 would now like to deliver its maximum shortcircuit current (about 1 A), but is properted from doing to by P1 P1 usually only has to pass the base drive current to T1 and T2 When there is a short, the voltage across it drops to such an extent that the output current of IC1 raduced to around 250 mA In addition the resistor prevents the thermal overload protection in IC1 from cutting in as this would produce a equare wave at the output

square wave at the output.

Obviously, things could go wrong if the negative bias voltage collapses while the main positive supply is still present (immediately after switching off, for instance). For this reason, T5 is added: it shorts the output of IC1 if the

negative supply fails.

Ga and C7 serve to 'Kill' high frequency components and they also improve the transient response. That is why these capacitors are not mounted on the board but directly across the output terminals. D6 and D7 are protection diodes. D6 will bypass ICl, should any irregularity in the load cause current to pass in the wornog direction. D7 prevents ICl from being blown up, if by chance the output of the power supply is connected to a voltage with the wrong polarity.

polarity. LED D5 has the 'cushiest' job of all the diodes: it merely acts as an on/off indicator.

Two versions

As we mentioned before, the transformers and bridge rectifiers have various possibilities, as the circuit can be built as either a single or a double power supply.

Double nower supply:

2 x 0 20 V/2 A

If two individual presttable voltages are to be available, the 'raw' supply section with the property of the available to be constructed as voltage to will also be constructed as voltage the will be apply and a (small) transformer Tr2 provides the supply and a (small) transformer tr2 provides the supply for (C2, Obytously, the double version will require two printed circuit boards, which are both constructed in the same manner and both include the Z-Y link. The points marked with an accent (A', etc.) belong to the second board.

Two separate supply voltages naturally allow for all sorts of combinations. This is illustrated in figure 3

Single nower supply 0 20 V/2 A

Single power supply 0...20 VZA

As figure 4 shows, a single power supply

involves fewer components and less

work. Only one transformer is now

required (although it must have a

double winding) and D1... D4 may be

omitted. In this case the Z-X link needs

to be made. Connecting B1 in the manner drawn in figure 4 provides IC1 with a positive voltage and IC2 with a negative voltage. In spite of the fact that the voltages are not equally loaded, the supply transformer will be under a symmetrical load.

#### Construction and setting-up

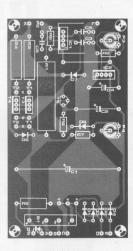

Figure 5 shows the printed circuit board for the power supply. A number of components are not mounted on the board: the supply transformer(s), the power transistors T1 and T2, the two

potentiometers and C6 and C7. T1 and T2 are mounted together on a heat sink with mica insulation. The heat sink must have  $1.7^{\circ}$  C/W thermal resistance, or less. These are available with pre-drilled holes (for  $2 \times TO3$ ). The wiring from the transistors to the circuit

1

Figure 3. A double power supply is clearly much more universal for experimental supply purposes.

Figure 4. An ordinary single power supply only requires one transformer.

#### Figure 5. The printed circuit board and component overlay of the universal power supply.

Parts list

Resistors: R1 =  $100 \Omega/9 W$ R2 = 2k2R3,R4 =  $0.68 \Omega/1 W$ R5 = 2k7R6 = 2k2/1 WR7 = 8k2

Capacitors: C1 = 4700 \( \mu/40 \) V C2 = 100 \( \mu/40 \) V C3 = 330 \( n \) C4 = 10 \( \mu/10 \) V C5, C6 = 100 \( n \) C7 = 22 \( \mu/35 \) V C8 = 10 \( n \)

R8 = 100 k

#### Semiconductors:

IC1 = 78 GU IC2 = 79 GU T1,T2 = 2N3055 T3,T4 = BD 139 T5 = BC 517 D1 ... D4,D6 = 1N4001 D5 = LED D7 = 1N5401 D8 = 1N4148

#### Miscellaneous:

P1 = 10 k, linear P2 = 1 k, linear P3 = 5 k preset P4 = 10 k preset S1 = mains switch

F1 = 2 A fuse, slo blo B1 = B40 C2200/3200 (40 V/2 A bridge rectifier)

Tr1 = 2 x 20 . . . 22 V/2 x 3 A transformer (figure 2) Tr2 = 2 x 12 V/2 x 50 mA transformer (figure 2) Tr3 = 2 x 20 . . . 22 V/2 x 1.5 A transformer (figure 4) board should be as short as possible and preferably of equal length. The base and collector connections to T1 and T2 all require their own leads to the board.

IC1 must also be provided with a heat sink, albeit a very small one. Please note: the power supply case may not be connected to the circuit's '0', It should only be connected to mains 'earth'. All that remains now is to calibrate the circuit. This can be done quite easily

with a good quality multimeter. Let's deal with it step by step: • Turn P3 and P4 to 0  $\Omega$  (fully anti-

- Turn P3 and P4 to 0 Ω (fully ant clockwise).

- Switch on (mains switch S1) and set P1 and P2 to minimum resistance.

Turn up P4 until 0 V is measured at

- the R7-P4-D8 junction.

Now turn P3 until exactly 0 V is measured at the output of the power

- supply.

P1 and P2 can now be used to adjust the output voltage between 0 and 20 V.

# intelekt

a sixteen-bit chess set

J. Kuipers

Do you play chess? Are you looking for an opponent who is always available . . . never gets impatient . . . plays a reasonably strong game . . . and even allows you to cheat a little, if you really want to? If so, it's time you met Intelekt!

So much for the advertising blurb. Actually, the chess computer described in this article does play a good game. It is designed around Intel's new 16-bit microprocessor, the 8088, which makes for reasonable speed and reasonable intelligence. Even at its 'stupidest' level of play (25 seconds per move) it will make a worthy opponent for many chess enthusiasts. At level three (out of eight), it thinks for five minutes or so per move — and provides what we considered a challenging game. Obviously, this evaluation is based to a large extent on our own chess skills. You can judge for yourself: some examples of actual games are included, with comments. If you feel that we played a stupid game, there are still five more intelligence levels to go; on the other hand, if the games look complicated, Intelekt would love to challenge you!

Chescomputers are no longer a novelty. This is surprising, when you think of it: a few years ago, it seemed unlikely that even big commercial computers could be taught to play a reasonable gamel By now, however, you can buy domestic versions for anywhere between £ 20 and £ 500. By and large, the "good" machines cost anything from £ 200 up.

To really determine the best value for money you would have to play several games against all the available chess computers. We have yet to find somebody who has done this! As 'secondbest evaluation', you can either play the machines against each other (with the risk that both play stupid moves without realising it) or else try them out on chess problems. The latter course in particular seems very popular for 'comparative reviews' in magazines In our oninion, this is a very second-rate approach: the fun and challenge in chess is not in solving 'mate in three' (when 'mate in four' is easy): the idea is to manneuvre your opponent into a position where you can 'mate' him! In other words, the fun is in playing the name - not in ending it

What is all this leading up to? Quite simple: if you want to know how 'good' Intelekt is in comparison with other chess computers ... we don't know! (Hurriedly:) But we get the impression that it's pretty good. We tried it out on chess problems that have been used in reviews. Where there was one obvious 'correct' move, Intelekt found it often even at level 1. Where there was an obvious move that led to mate in four or five and an unexpected one that gave mate in three, it invariably selected the 'obvious' move. However, we played games against a few commercial machines that scored highly in reviews, and found them rather unexciting; we played against Intelekt and it was good

fun. To sum up its strong points in a few nutshells:

- it is easy to set up any position (even halfway through a game);

illegal moves are not accepted:

- it knows all the rules of the game; castling, for instance, is obviously taken into account as a 'possible move';

- move';

it can play either black or white (or even both sides!):

- it knows the value of sacrificing a piece to gain positional advantage: not only will it ignore this kind of 'sacrifice', it will even propose them where this seems worth trying:

- it plays a good game. This, in our opinion, is what counts.

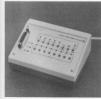

Who or what is Intelekt? He (or it) is an electronic circuit containing a microprocessor and a chess program (in ROM), with an input/output that must be connected to a 'terminal' - the 'Elekterminal' (Elektor, November/ December 1978), for instance, You

make your moves by entering them on the keyboard of the terminal; Intelekt answers by displaying the board, his moves and comments (!) on a TV screen, via the same terminal. In other words, Intelekt is a brain; to speak to him and receive his replies you also need a 'terminal'.

terminal.

In this article, we will give a brief description of the "hardware" that is involved (circuit and printed circuit board) but no indication of the 'software' (the actual program). Instead, we will attempt to give as clear an impression as possible of his chess skills. After all, that is what counts.

#### The hardware

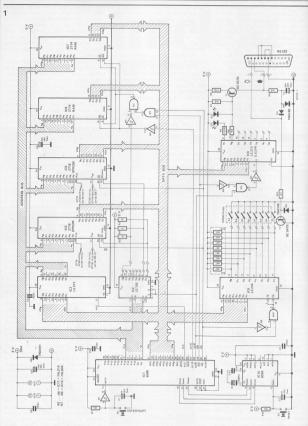

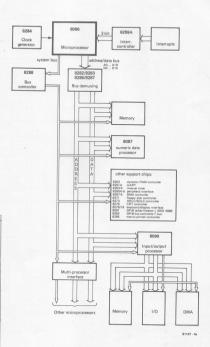

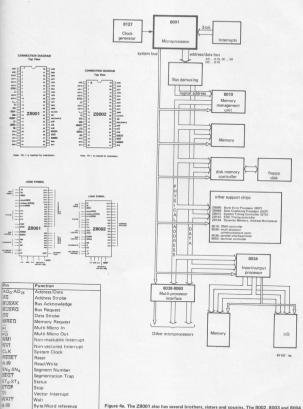

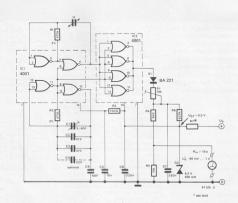

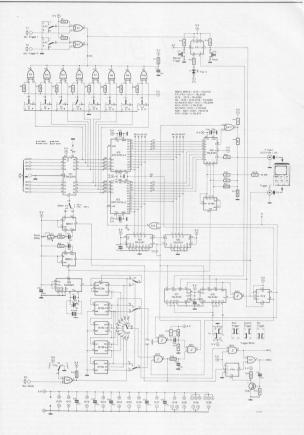

The complete circuit is shown in figure 1. It is not our intention to discuss it in minute detail, but we will attempt to paint a sufficiently clear overall picture.

picules. To sast with the "16-bit brain" (the 8088): this microprocessor can run in either minimum or southern minimum or southern minimum or southern minimum or legic level at pin 33. As the words indicate, maximum mode is intended for large systems and minimum mode for little ones. Intelekt belongs in the latter category. As explained in the supplement on 16-bit microprocessors, the 8088 produces the bus control signals itself when it is set to minimum mode; in maximum mode, a further IC would be needed to control the (more extensive) bus.

Inside the CPU itself, data is handled as 16-bit words. However, the data bus that connects it to the outside word is only 8 bits wide. This means that each 16-bit word must be cut into wa 8-bit bytes before it can be put on the data bus. For obvious reasons, these two chunks of data are transmitted one after the other — not simultaneously ...In other words, they are 'time

multiplexed'.

In actual fact, things are even more complicated. When Intel introduced the 8085 (a 'normal' 8-bit microprocessor), they used a single set of pins for a multiplexed address/data bus. Now, in the 8088, they've used the same system: the lowest eight address bits also appear

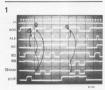

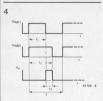

Photo 1. Some of the main control signals, as they appear on the screen of a normal oscilloscope.

on what we have so far called the data bus. This saves pins, making for a smaller and cheaper IC package, and the information is still available at the exact moment that it is required. First the address bits, obviously (the ALE pin indicates that a valid address is being output); then the data, in two 8-bit churks.

crunks. Having saved seven pins (the eight multiploxed pins are saved, but ALE must be added), any normal designer immediately starts wondering what he can dwith them. Apparently, finel designers with the property of the pins of the pins for interrupt signalling; now, in the 908 we find the address range has been extended to 1 Mbyte (one million bytes of memory!).

If the special Intel memory ICs are used, seven tracks can also be saved on the printed circuit board. However, we decided against this; instead, the data and address buses are separated by means of an octal latch (IC3), so that the address information is always available and normal memory ICs can be used.

If all this seems complicated take a look at photo 1. This shows a group of signals, as they would appear on a 'normal' oscilloscope (not 'cleaned up' by a logic analyser). The upper line is the clock, ticking over at 5 MHz (!); all further timing is derived from this. At point ① the processor has transmitted the new address information. One of the address/data outputs (ADO) is shown as the second trace. This is followed immediately by the ALE pin (third trace) going high, indicating that a valid address is now present at the output of the CPU. The corresponding output from the address latch (IC3) is shown as the fourth line from the top; as can be seen, each time ALE goes high this output assumes the same level as that on the ADO line, and holds it until the next ALE pulse appears.

If the processor now intends to 'read' data, it sets pin 32 (RD) to a low logic level as can be seen in the fifth trace on the photo. When the data is to be read from EPROM, the correct chip has already been selected by the proceding already been selected by the proceding to the OE pin (output enable) of both to the OE pin (output enable) of both EPROMs, so the selected memory chip will now put the desired data on the bus (at  $\odot$  on the second trace). The processor 'reads' this data and immediately returns the RD pin to a high logic level. It can now put the next address on the bus, after which the whole cycle is

When reading from RAM, the basic principle is the same. However, this type of memory does not include an 'output enable' pin, so the read (or write) signal is included in the 'chip select' logic (CS).

Writing into RAM is similar to reading. As before, the first step is to select the address. Then, immediately after the negative-going edge of the ALE

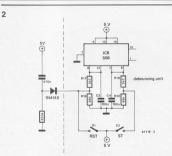

Figure 1. The complete circuit of Intelekt. The terminal is connected as shown at the lower right-hand corner in the circuit. Note that an interrupt key is included, although this is not required for operating the chess computer.

pulse, the processor puts the data onto the AD lines (0). It then sets WR at logic 0 (the sixth trace on the photo) to indicate that the data is valid. This 'write' signal is combined with the address information; the correct address set of the data is stored in RAM. The data on the bus remains valid for the complete duration of the

So far, so good – but how is the RAM to know whether it is to transmit or receive data? This is where the DT/R signal comes in ('data transmit/receive'; the lower trace in the photo). As the address information goes out, this pin is set to logic 1 for a write cycle, or to logic 0 for read. It is passed through an inverter to drive the WE (write enable) inputs to the RAMs.

#### One address in a million

Although the 8088 can handle over one million addresses, Intelekt only needs a good 16,000. Obviously, things would tend to get confusing if several 'chins' started to 'talk' at once At any given moment the CPLI should only be in contact with one memory IC and this is where the address decoder (IC2) comes in This IC monitors three of the address lines (A11 A13) and converts them into eight chin-select signals Depending on the address range indicated one of these chin-select signals goes to logic 0 and the corresponding memory IC can communicate with the CPU via the data bus. If the processor wants to talk to an input/output IC it sets the 10/M line to logic 1, deactivating the address decoder

The address decoder has open-collector outputs. This simplifies matters if several outputs are to be combined—for instance when using larger EPROMs in some future updated version. Each output defines a 2 k address block, so two of these blocks would have to be corresponding pins of the address decoder together) if a 4 k EPROM, type 2732, is to be used.

Although the RAM chip used (the 2114) is only a 1 K type, there is no reason why it should not be allocated its own 2K block of addresses, (Note that the two 2114s each take care of four data bits; together, they form the 1 K x 8 memory). As shown in figure 2, the RAM is located at the lowest memory addresses—from 00000 003FF. Since it is enabled during the complete 2 K block, a duplicate RAM area appears from 0000 to 07FF. In other complete 2 K block, a duplicate RAM see appears from 0000 to 07FF. In other complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM for the complete 2 K block, a duplicate RAM f

The input/output (I/O) chips IC8 and IC9 don't need an address decoder. All I/O write instructions enable IC8, via the combined 10/M and WR signals; similarly, all I/O read operations refer to IC9.

#### Allocating the addresses

One might assume that EPROM and

FEEFE EPROM I (2K)

FE000 Umased

FC7FF duplicate

RAM (1K)

FC000 G2X

idem

Figure 2. The 'memory map'. Although the theoretical address range is 1 Mbyte, it actually consists of 64 identical 16 Kbyte sections.

RAM could theoretically be located anywhere in memory. In practice, this is not quite true. When the processor is reset, it starts to run a program from address FFFF0 on. To make sure that there is a program there, it is advisable to locate an EPROM in this final address block.

Furthermore, after an interrupt, the processor goes looking for an 'interrupt vector' (this is the address where the corresponding interrupt routine is located) at one of the lower memory addresses. Since it is useful to be able to change these addresses, RAM must be located in the lowest address block. Even though Intelekt doesn't actually make use of the interrupt facility, it was decided to locate the memory at the 'normal' addresses. This leads to the situation shown in figure 2: RAM (with its duplicate) in low memory, and two blocks of EPROM (4 k in all) at the top. All this may seem quite reasonable,

All this may seem quite reasonable, until you start thinking it over. EPROM is at the top and RAM at the bottom of a one mega-byte address range — but the address decoder is only defining eight 2 K blocks of memory! How can 16 K be equal to 1 M?

Since we are now tossing out K's and

M's at the rate of one or two in each sentence it is perhaps a good idea to digress briefly and explain what they signify Using a single address line you could distinguish between two addresses With two lines you get an 'address range' of four addresses: three lines define eight addresses, and so on, By the time you get up to ten lines you find that you can distinguish between 1024 adresses This is referred to as a '1 K block' Since it is slightly more than one thousand we use a capital K. It's rather like the difference between Imperial and US gallons: they're both gallons. but one is slightly more than the other Similarly, the 1 Mbyte address range of the 8088 is slightly more than one million addresses: 20 address lines define 1 049 576 addresses

Back to our 'groblem': how can 16 K be equal to 1 M? Fourteen address lines define a 16 K block; of these lines, the highest three (A11... A13) go to the address decoder. All higher address lines are simply ignored 17 his means lines are simply ignored 17 his means difference between addresses. 0000, 0000, 0000 and so on, 17 his can be seen in table 1, where the actual bits on the various address lines are shown for these addresses. Reading from left to right, these bits are used as follows:

A19 . . . A14 are ignored. They can have any value, without making any difference to the actual memory location that is selected.

A13...A11 go to the address decoder. They define eight 2 K blocks; the highest two enable the EPROMs, and the lowest 2 K block is for the RAM.

A10...A0 define the 2048 addresses in each 2 K block. In the lowest (RAM) block, A10 is also ignored; this means that the same RAM is addressed in both the first and second 1 K block (these are referred to as 'RAM' and 'RAM duplicate', respectively).

The answer to the 'problem' should now be clear: the basic 16 K address range is simply duplicated 64 times in the total 1Mbyte range, as shown in figure 2. After reset, the processor looks at address FFEPO. The address decoder looks at lines A11 to A13, finds them the control of the contro

#### Interface

Communication with the outside world runs over a simple RS-232 interface (T1 and T2). The 'receiver' is a single transistor that converts the input signal levels to TTL logic levels:  $-12\ldots -5 \ V = logic \ 1 \rightarrow +5 \ V;$

+5 . . . +12 V = logic 0 → 0 V.

Diode D5 protects the transistor when the input signal swings negative. The 'transmitter' end is also a single

The 'transmitter' end is also a single transistor. This one operates as a voltage-to-current converter, which

4-14 - elektor april 1981

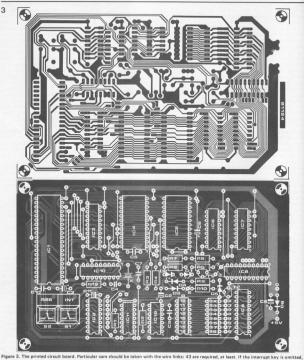

a further wire link is required to connect what would otherwise have been the centre contact pins, as shown. The same applies for the reset key. if this is mounted off the board or replaced by a type that does not contain this internal connection. Where several wire link options are possible. for other memory ICs, only the correct link is shown.

Parts list DIP resistor network) D3 . . . D5 = 1N4148 IC10 = 8284 IC11 = 74LS14 D6 = 1N4001 or surge diode Capacitors (TVS 505, for instance) IC12 = 74LS00

T1 = BC 557B

T2 = BC 547B

IC2 = 74LS156

IC1 = 8088

C4 = 10 p R2,R3,R4 = 1 k R5 = 220 Ω C5,C7,C9,C10 = 100 n R6,R7,R9 = 1k8 R8 = 47 Ω R10 = 4k7

Resistors:

R1,R19 = 10 k

D1 = LED R11 . . . R18 = 8 x 4k7 (or 16-pin D2 = LED (red) IC9 = 74LS244

$C1.C3 = 1 \mu/16 V Tantalum$

C2,C6,C8 = 10 µ/16 V Tantalum

IC3,IC8 = 74LS373 IC4,IC5 = 2716 EPROM 450 ns IC6,IC7 = 2114 RAM 450 ns

S1 = digitast switch or wire link S2 = digitast switch \$3 . . . \$9, \$x = 14- or 16-pin DIP switch (or wire links, see text)

X1 = 15 MHz crystal small size HC-18/U

Miscellaneous:

(see text)

automatically makes it short-circuit proof LED D2 is used to set the base voltage - it will harely light since the current through it is only 2 mA. To meet the RS-232 standard a negative output voltage is also required. Since Intelekt only uses a positive supply, a little trick is used. The input signal. coming from the terminal printer or whatever, swings between positive and pagative levels. This signal is rectified (by D3 D4 and C2) to provide the negative 'supply' for the output.

A second output from IC8 drives LED D1 This LED flashes on and off when the chess program is running. Regular and fairly rapid flashes indicate that he is waiting for you to enter data: slower flashes (corresponding to the depth of the 'search') will appear when he is thinking

Of the eight inputs to IC9 one is used for the RS-232 input. The others can be connected to a DIP switch; this is a unit that contains seven or eight miniature switches, and can be plugged into a normal IC socket Note that if an eight-switch version is used the lower switch should not be closed - otherwise it would short the RS-232 input to ground! Three of the switches set the haud rate as listed in table 2 Obviously for a fixed haud rate (atransmission speed to and from the terminal) wire links can be used instead of the switches.

#### Construction

The printed circuit board is shown in figure 3. To keep the cost down to a reasonable level, it was decided to use a single-sided board. This does lead to a larger number of wire links. There are 43 in all and it's worth counting them before switching on for the first time! The possibility of future extensions was also considered and some points were brought out even though Intelekt doesn't use them. However, this does not mean that the hoard can be used as the basis for an extensive system: the bus is not buffered, and the addresses are not fully decoded. The only possible extensions we have in mind are the use of other EPROMs (or ROMs) with a 4 K range, and extension of the RAM area by substituting a 4118, say, for one of the EPROMs. In general, the flexibility that the board offers is only intended to facilitate its use in other small-system applications.

The main wire links to watch in this connection are:

- · those at each EPROM socket: they determine whether a 2716, 2732 or 4118 can be used - for Intelekt, the '2716' link is used

- . the chip enable (CE) inputs to the EPROMs and RAM are connected to the address decoder as required; for Intelekt, EPROM 1 is driven from output 7, EPROM 2 from output 6 and RAM from output 0.

- . the DIP switch (or wire links) set the

Table 1

| Address       |    |    |    |    |    |    |    |    |    | ary) |   |   |   |   |   |   |   |   |   |   |

|---------------|----|----|----|----|----|----|----|----|----|------|---|---|---|---|---|---|---|---|---|---|

| (hexadecimal) | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10   | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 00000         | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 03FFF         | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1    | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 04000         | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 08000         | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| FC000         | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|               |    |    |    |    |    |    |    |    |    |      |   |   |   |   |   |   |   |   |   |   |

Table 1. Of the 20 address lines, only the lower 14 are actually used. A11 ... A13 are passed to the address decoder to determine which memory chin must be enabled. The logic levels of the higher address bits (A14 ... A19) are irrelevant.

Table 2 4 Se Se S Boud I roto 9600 4900 2400 4000 600 200 150

Table 2. The baud rate (transmission speed in hits per second) is determined by the setting of three of the switches in the DIP switch block. If a fixed rate is sufficient, wire links can be used instead.

baud rate: it is set according to table 2

Two digitast switches are also mounted on the board. Note that, on this type of switch, the centre contact is brought out onto two pins. This fact is used on the board to connect 'supply common' to a whole section of board, If other types of switches are used or if the switches are mounted off-board, two further wire links will be required at this point!

#### Communicating with Intelekt As explained earlier. Intelekt is con-

trolled via the keyboard of a terminal and he 'talks back' by means of the associated display (TV screen or printer). To get some idea of how this works in practice, assume that Intelekt is connected to the Elekterminal. After switching on, first operate the

Reset key on the chess computer itself - note that this is the only command that is not entered via the Elekterminal keyboard. Intelekt will respond by displaying the following message: TINY CHESS VI.O

#### LEVEL IS 1 CHANGE TO .

You can now enter a '1', followed by Carriage Return - the 'why' of this will be explained later on. The chess board will now appear on the screen, in the

Figure 4. The initial board position, as it will annear on the screen. The single letters (R. N. B. . . . ) are white pieces: the letter pairs are black: the dots (;;;) indicate a vacant white square.

initial position as shown in figure 4. The single letters (R. N. B....) stand for the white pieces, the letter pairs (RR, NN. etc) are black pieces and the dots (:::) are empty white squares on the hoard Intelekt then asks for your first move:

To enter your move, key in:

- the square containing the piece that

- is to be moved:

- a space:

01111

- the square to which the piece is to be moved:

- Carriage Return. Intelekt will now check whether or not you have entered a legal move (if not, he will request a new entry) and then proceed to calculate his response. Initially he will invariably find a response in his 'book of standard openings' and reply immediately. Later on, when he has to start thinking out his moves, the response time can vary from 25 seconds (lowest level of skill) up to several hours (highest level), Having worked out his move, Intelekt will print it on the screen, and immediately display the new position on the board. The result so far could look like this (bold type: your moves):

TINY CHESS VI.O. LEVEL IS 1 CHANGE TO 1

(initial board situation)

01W: e2 e5 (CR) - an illegal move so: 01W: 62 63 (CR)

01W . 62 64

(new board situation)

- waiting for your next move If you notice a typing error before entering Carriage Return it is possible to correct this by operating 'Rackspace' However if it was a legal move and you have already typed Carriage Return there is no easy way to correct it If you really want to cheat it is possible to enter an illegal move provided you terminate it with 'I ine Feed' instead of 'Carriage Return'

When it is your move, you can also enter one of the following instructions: Control X: change players. You now play black; he responds by printing 'my move' After he has made his move you can change back to playing white by again entering Control X

Control A: autoplay He plays both sides

Control N: to set the 'number' of the level that you want to play. He responds with 'Level is 1 change to ' (assuming that you were at level 1): you can then enter any number between 1 and 9 followed by Carriage Return, Level 1 is the easiest and level 8 the most difficult We found level 3 to be a good compromise between response time (about 5 minutes, on average) and skill,

Control C: change board mode, Intelekt responds with a dash prompt: '-'; you can now enter one of several commands:

· erase the board (remove all nieces) by entering Control E.

change any square, as follows: - enter the number of the square

(h5 say). Intelekt responds by printing what is on that square: - if desired, update the square by

entering either a colon (:) to empty the square, or a single letter (K. Q. R. B. N or P) for the corresponding White piece or two letters (KK, QQ etc.) for a Black piece:

- enter a Space to step to the next square (whether or not you have undated the preceding one):

- enter Carriage Return when a sequence of squares has been updated. Intelekt again responds with a dash prompt, waiting for you to enter a new square.

· after editing the board, return to normal mode by entering Carriage Return. It may be worth noting that Intelekt will refuse to play unless there are a Black and White king on the board . .

All the commands listed above can only be entered when it is your turn. So what do you do when Intelekt is thinking? You can 'interrupt' him by entering Break or several spaces. This has the same effect as the Control N instruction described above: you can change the level of play. By entering a lower level (level 1, say) you can ensure that it will be your turn within half a minute: at

that point you can of course enter any

Reset: This resets the board and program for a new game

#### Special moves

Entering 'normal' moves was explained above For those who are not so femiliawith the numbering of the squares (A to H left to right, and 1 to 8 from bottom to ton) each hoard print-out includes these letters and numbers. There are also a few special moves: castling en passant taking of a nawn check and pawn promotion. All of these possibilies are known to Intelekt. They are dealt with as follows:

Castling: only enter the move for the king. Intelekt will interpret this correctly check whether or not it is nermissable and then move both king and rook accordingly

En-passant: this move is not as well known as it ought to be. To put it in a nutshell: when a nawn is initially moved up two squares passing a square that is attacked by a nawn it can be taken at the next move by that nawn As an example assume that Black has a nawn on b4. If white moves a nawn a2-a4 Black can take it immediately by moving b4-a3. To execute this move. you would simply enter 'b4-a3'. Intelekt will know what is meant,

Check: Intelekt will print a warning when it places you in Check for Checkmate): it then rejects any move that doesn't remove your king from check Stalemate is also recognised

Pawn promotion: It is presumed that when you promote a pawn, you want a queen; and Intelekt calculates its moves on this basis (a minor 'blind spot'). If you want anything else this can be obtained via the 'change board' mode.

#### A few games

Three complete games are given in tables 3 . . . 5. In the first, fairly straightforward game, Intelekt played black: in the second he played white In the third game. Intelekt again played black: furthermore, in this game white made a deliberate effort to 'draw out' the machine as far as possible before striking back - too late as things turned out

Obviously, it would take up too much snace to examine each game in great detail. However, if you are interested in playing out each game according to the moves listed in the corresponding table we will attempt to nick out the interesting highlights.

#### Game 1

The first two moves were according to his opening 'book': Black's response was immediate. White's third move (q2-q3) put a stop to this; from now on. Intelekt must start thinking for himself . . .

After some manoeuvering and minor skirmishes. White's move 13, f2-f4 was a deliberate attempt to make things complicated. If, on the next move, White takes one of Black's pawns If4ve5 or f4xa5) the rook on f1 would attack Black's guess and things would start to hannen Black can't take the pawn by playing e5xf4, and a5xf4 onens a lot of interesting possibilities

In fact things developed nicely. Then at the 17th move White was faced with the choice: Nd5-f4 or attempt to break un Black's central nawn formation? He chose the latter ontion but it didn't quite work out as planned Not yet anyway. Moves 20 and following may seem

rather strange at first sight 20 Ra1-d1 is safe enough: Black can't play Rh5xd1 since this would be followed by Of2xf7 mate! To remove this threat Black tried f7-f5. This led to the loss of a pawn, and White even got the opportunity to continue the

#### Table 3

1 e2.e4 c7.c5 c2.c4 3 02-03 d7-d6 4 Bf1-02 97.96 5 Nh1 o2 NINO OF 6 d2d3 Nr6.d4 7 No1-e2 Bc8-d7 0 0 0 Bd7-q4 Nd4xe21 9 h2.h3 10 No2vo2 040 (6 Bc1.h2 97-95 12. Od1-d2 Ba4-e6 13 f2-f4 o5vf4 14 Ne2vf4 Be6-q4

15 NIFA dE 010 40 16 Od2.f2 of vhd 18 d3-d4 h4-h3? 19 a2vh3 Bf8-07 20 Palidi 47.45 Bh5-q6 Of2xf5 Ba6-h5 22 Off. f2 22 a3-a4

Bh5-o6 24 h2-h4 Na8-b6 25 04-05 Nh6-087 26 daya6 Bo6-h5 27 e5xd6 Ba7yb2 28. Qf2xb2 Bh5xd1 20 Ohouho Dallub2

30. Qh8xq8<sup>†</sup>? Ke8-d7 31. Qa8xh7† Kd7xd6 Nd5-b62 Qd8xb6<sup>†</sup> 32

Kg1-h1 22 34 Bf1-f6<sup>†</sup> Bc4-e6 Rf6xe6<sup>†</sup>I 35 KHEVOR

36. Qh7-h6<sup>†</sup> Ke6-f7 37 Ohfiyhfi "I knew that"

Ra8.h8 38. Qb6-f6<sup>†</sup> Kf7-q8

39. g5-g6 Rh8xh4<sup>†</sup> 40. Qf6xh4 Kg8-g7 41. Qh4-h7<sup>†</sup>

"GRRR" Ka7-f6 42. g6-g7 b7-b5

43. g7-g8 (Q) "I knew that "I give up"

Table 3. The first game, with Intelekt playing black.

'mopping up' action in the centre (moves 26 and following). During a momentary lull in the battle, Black decided it would like to take a pawn (29)

... Bd1xb3], leaving White with so many options that he didn't know which to choose! Nd5-27!, followed by Qh8xg81, might well win a rook. On the other hand, Qh8xg84 seems quite promising already, Or Qh8xh77 Or Rf1-b17 Or e4-65! The game had already lasted three hours, so White decided to pick one alternative at random.

32 Nd5-b6 was a mistake, pure and simple. The idea was to pin things in that corner (208k:b6 was to be followed by Rf1-f6, and f6 Black tried to save this rook, White could follow up with Rf1-df), but White forgot that Ob6 gives check! Amazingly, Intelekt offerad this option one move later—apparently some of the property of the specific transverse of the specific transv

What followed was just a fairly brutal end-game, punctuated by various comments from lotelekt

#### 0----